### **General Description**

The DM562P integrated modem is a two-chipset design that provides a complete solution for state-of-the-art, voice-band Plain Old Telephone Switching (POTS) communication. The modem provides for Data (up to 56,000bps), Fax (up to 33,600bps), Voice and Full Duplex Speaker-phone functions to comply with various international standards.

The design of the DM562P is optimized for desktop personal computer applications, embedded microprocessor applications and Multi-Function Peripheral (MFP) FAX application. It provides a low cost, highly reliable, maximum integration, with the minimum amount of support required. The DM562P modem can operate over a dial-up network (PSTN) or 2 wire leased lines.

The modem integrates auto dial and answer capabilities, asynchronous data transmissions, serial and parallel interfaces, various tone detection schemes and data test modes.

The DM562P modem reference design is pre-approved for FCC part 68 and provides minimum design cycle time, with minimum cost to insure the maximum amount of success.

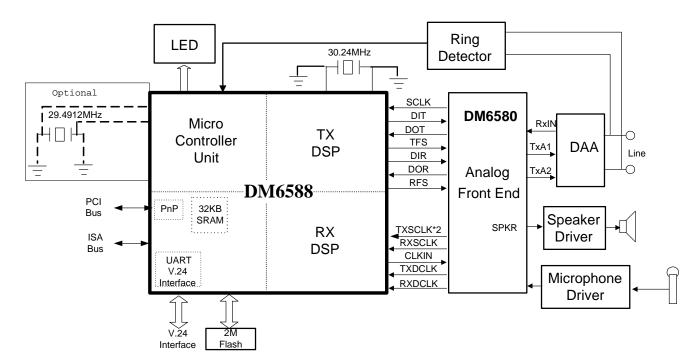

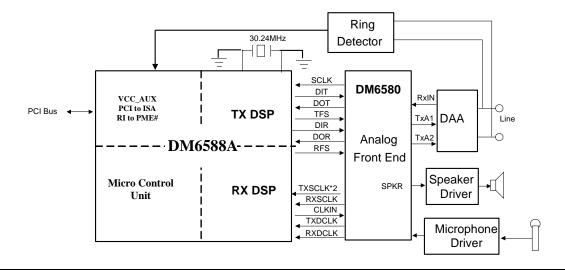

The simplified modem system, shown in figure below, illustrates the basic interconnection between the MCU, DSP, AFE and other basic components of a modem. The individual elements of the DM562P are:

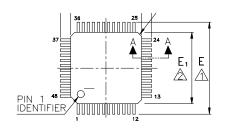

- DM6580 Analog Front End (AFE). 48-pin LQFP package.

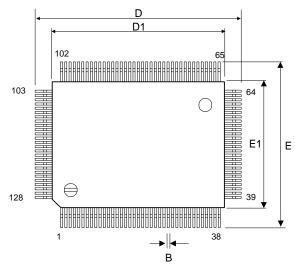

- DM6588 ITU-T V.90 integrated Processors with 32K bytes SRAM built in 128-pin QFP package

## **Block Diagram**

Final Version: DM562P-DS-F01 February 02, 2004 1

40

# **Table of Contents**

| General Description 1                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                           |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|

| Block Diagram 1                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                           |

| Features 3                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                           |

| Chipset<br>Chip 1: DM6588 Modem Controller Unit<br>with PnP                                                                                                                                                                                                                                                                                                                                                                                                       |                                           |

| DM6588 Description 4 DM6588 Block Diagram 4 DM6588 Features 4 DM6588 External Pin Configuration 5 DM6588 ISA Pin Configuration 6 DM6588 PCI Pin Configuration 7 DM6588 Pin Description 8 DM6588 Pin Description-ISA interface only 1 DM6588 Pin Description-PCI interface only 1                                                                                                                                                                                  | 1                                         |

| DM6588 Functional Description 1. Operating Mode Selection 2. Micro-controller Program Memory 3. Micro-controller Power Down Mode 4. Enhanced Internal Direct Memory 5. Re-flash Program Memory 6. Micro-controller I/O Description 7. HDLC Description 8. Micro-controller Control Register for Internal Mode 9. Host Control Register for Virtual 1550A UART 1 10. Micro-controller Control Register for PCI Interface 11. PCI Configuration Register Definition | 4<br>4<br>4<br>4<br>4<br>4<br>6<br>7<br>7 |

| DM6588 External Electrical Characteristics DM658A External Absolute Maximum Ratings DM658A External DC Characteristics DM6588 ISA Electrical Characteristics DM6588 ISA Absolute Maximum Ratings DM6588 ISA DC Characteristics DM6588 ISA AC Characteristics & Timing Diagrams DM6588 PCI Electrical Characteristics                                                                                                                                              | 5<br>5<br>6<br>6<br>7                     |

| DM6588 PCI Absolute Maximum Ratings DM6588 PCI DC Characteristics DM6588 PCI AC Characteristics & Timing Diagrams 33                                                                                                                                                                                                                                                                                                                                              | 8<br>8                                    |

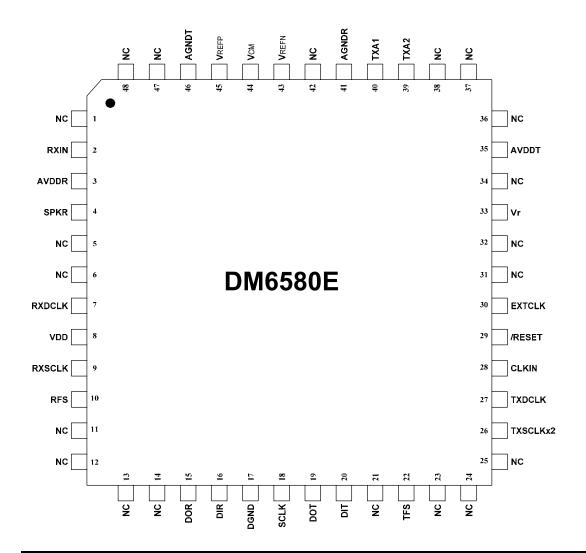

# Chip 2: DM6580 Analog Front End

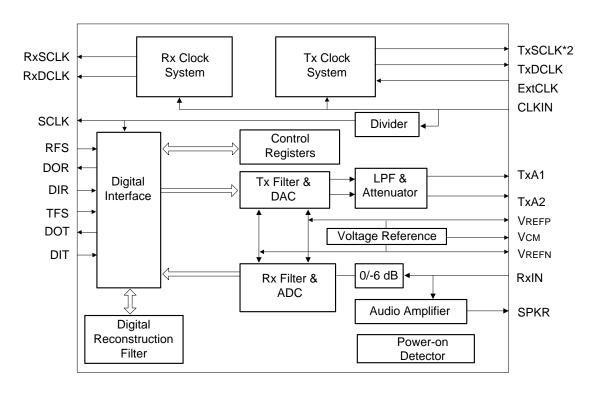

DM6580 Description

| DM6580 Block Diagram                        | 40 |

|---------------------------------------------|----|

| DM6580 Features                             | 41 |

| DM6580 Pin Configuration                    | 41 |

| DM6580 Pin Description                      | 42 |

| DM6580 Functional Description               | 43 |

| DM6580 Register Description                 | 43 |

| DM6580 Absolute Maximum Ratings             | 44 |

| DM6580 DC Characteristics                   | 44 |

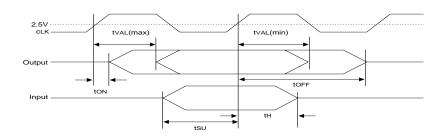

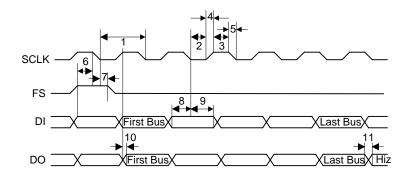

| DM6580 AC Characteristics & Timing Diagrams | 45 |

| DM6580 Performance                          | 45 |

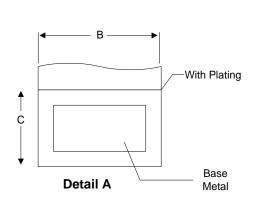

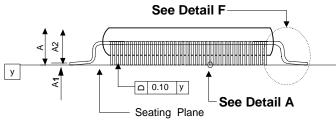

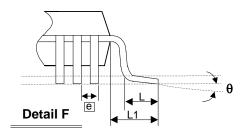

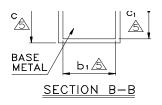

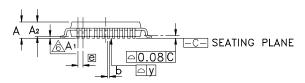

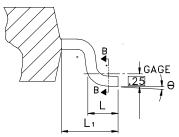

| Package Information                         | 47 |

| Ordering Information                        | 48 |

| Company Overview                            | 48 |

| Contacts                                    | 48 |

|                                             |    |

Final Version: DM562P-DS-F01

February 02, 2004

#### **Features**

- Data

- ITU-T V.90 (56000 to 28000 bps)

- ITU-T V.34 (33600 to 2400 bps)

- ITU-T V.32bis (14400, 12000, 9600, 7200, 4800bps)

- ITU-T V.32 (9600, 4800bps)

- ITU-T V.22bis (2400, 1200bps)

- ITU-T V.22 (1200bps)

- ITU-T V.23 (1200/75bps)

- ITU-T V.21 (300bps)

- Bell 212A (1200bps)

- Bell 103 (300bps)

- Fax

- ITU-T V.17 (14400, 12000, 9600,7200bps)

- ITU-T V.29 (9600, 7200bps)

- ITU-T V.27ter (4800, 2400bps)

- ITU-T V.21 Channel 2 (300bps)

- Group III. Class 1

- Support ECM mode

- **Data Error Correction**

- MNP Class 4

- ITU-T V.42 LAPM

- **Data Compression**

- MNP Class 5

- ITU-T V.42bis

- Voice compression

- 4 bit ADPCM (ITU-T)

- 2, 3 an 4 bit ADPCM (Davicom proprietary)

- 8 Bit PCM

- **DTE Interface**

- DTE speed up to 115200bps

- Enhanced "AT" command set and S registers

- TIA/EIA 602, ITU V.25 ter AT command

- TIA/EIA 602, ITU V.25 ter AT command

- TIA/EIA 578 Fax Class 1 command set

- TIA/EIA IS-101 Voice command set

- Integrated UART 16550

- Parallel (ISA/PCI) and Serial (UART) interfaces

- 6, 7 and 8 bit character support

- Even, odd, mark and none parity detection and generation

- 1 and 2 stop bit support

- Auto DTE data speed detection through "AT"

- Support FSK Caller identification (Caller ID)

- Speakerphone

- Selectable world wide call progress tone detection

- Enhanced 8032 compatible micro-controller

- Power down mode

- Access up to 256K bytes external program memory

- Access up to 64K bytes external data memory

- NVRAM to store two user configurable, selectable profiles with three programmable telephone numbers

- 32K bytes SRAM built in

# Parallel bus for embedded microprocessor

Compatible to ISA bus

#### PCI internal modem only

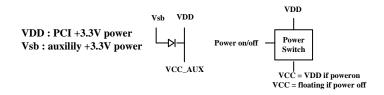

- PCI Plug and Play (PnP) support

- Compliant with PCI specification 2.1

- Compliant with PCI bus Power Management Interface Specification revision 1.0

Version: DM562P-DS-F01 February 02, 2004

Final

## Chip 1:Integrated Processor Unit with PnP

### **DM6588 Description**

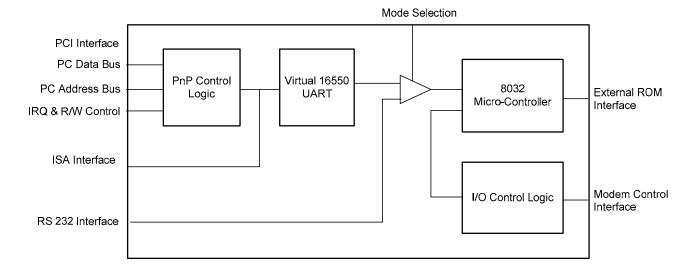

The DM6588 Modem Control Unit is designed for use in high speed internal and external modem applications. The DM6588 incorporates a 80C32 micro-controller, a virtual 16550A UART with FIFO mode, and Plug & Play control logic.

The DM6588 MCU performs general modem control functions, and is also designed to provide Plug and Play capability for PCI bus systems.

### **DM6588 Block Diagram**

#### DM6588 Features

- Control interface support

- Supports parallel and serial interfaces

- Includes a 80C32 micro-controller

- 256K bytes maximum external program memory

- 64K bytes data memory built in

- Provides automatic Plug and Play or software configuration capabilities

- Virtual 16550A UART compatible parallel interface

- Fully programmable serial interface:

- 6, 7 or 8-bit characters

- Even, odd, mark and none parity bit generation and detection

- 1 and 2 stop bit generation

- Baud rate generation

- Includes I/O control logic for modem control interface

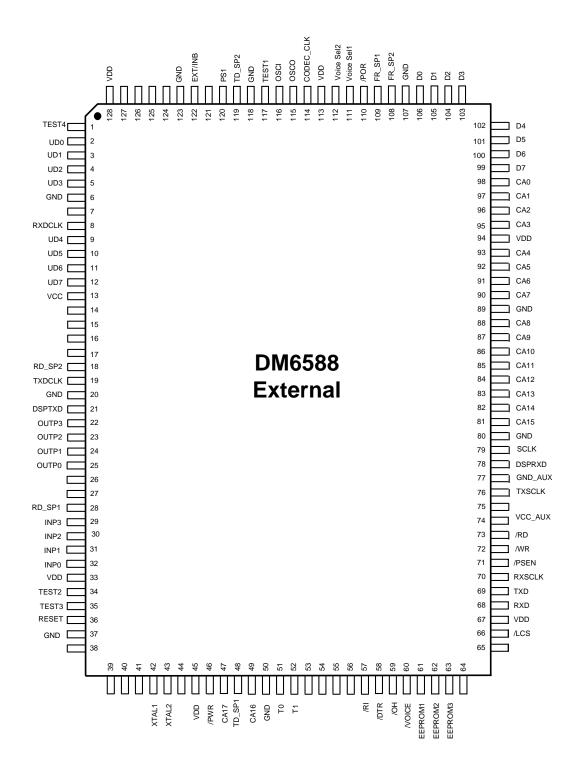

# **DM6588 External Pin Configuration**

Final Version: DM562P-DS-F01

Version: DM562P-DS-F0<sup>-7</sup> February 02, 2004

6

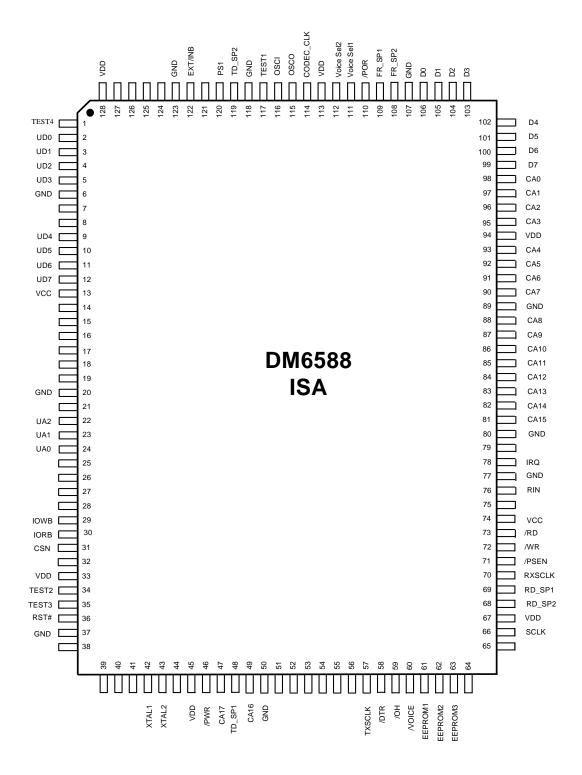

# **DM6588 ISA Pin Configuration**

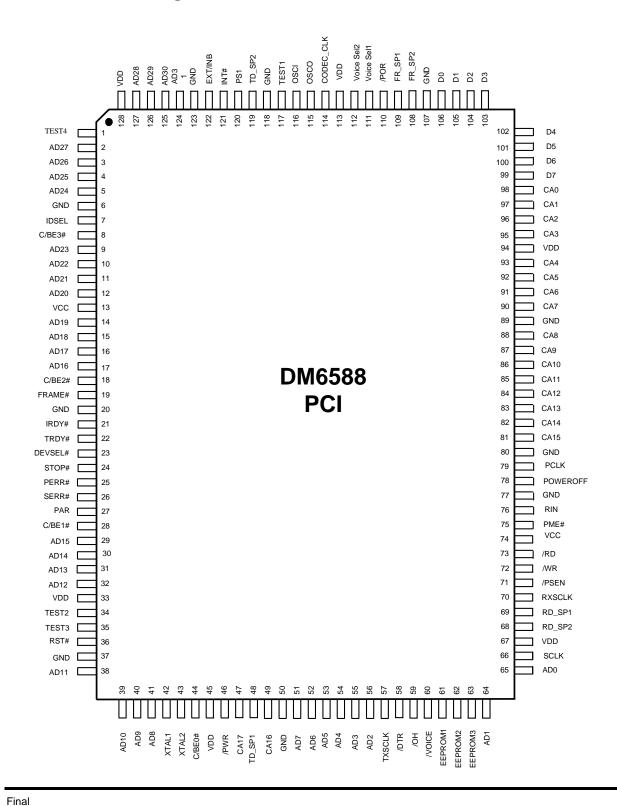

## **DM6588 PCI Pin Configuration**

Version: DM562P-DS-F01

| Pin No.                                    | Pin No.                                | Pin No.                                    | Pin Name                            | I/O | Description                                                                                                                                                         |

|--------------------------------------------|----------------------------------------|--------------------------------------------|-------------------------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| External                                   | Internal<br>PCI                        | Internal<br>ISA                            |                                     |     |                                                                                                                                                                     |

| 1                                          | 1                                      | 1                                          | TEST4                               | I   | Test pin 4, normal ground. External: N/C (low). PCI: N/C (low). ISA: connect to 3.3V.                                                                               |

| 2,3,4,5,<br>9,10,11,<br>12                 |                                        |                                            | UD0 - UD7                           | 0   | Modem Control Output, for external modem: Memory address mapping of the controller is E800H.                                                                        |

| 8                                          |                                        |                                            | RxDCLK                              | I   | Receive Data Rate Clock:(External)  This pin is used as reference clock of DSPRXD pin.                                                                              |

| 18                                         | 68                                     | 68                                         | RD_SP2                              | I   | Data Input Pin Of The Serial Port 2: The serial data is sampled at the falling edge of the SCLK. The MSB is coming immediately after the falling of FR_SP2 signal.  |

| 19                                         |                                        |                                            | TXDCLK                              | I   | Transmit Data Rate Clock:(External) This pin is used as reference clock of DSPTXD pin.                                                                              |

| 21                                         |                                        |                                            | DSPTxD                              | I   | Modem Transmit Data (External) Shifted into DM6581/DM6582 from EIA port through this pin at the rising edge of TXDCLK.                                              |

| 28                                         | 69                                     | 69                                         | RD_SP1                              | I   | Data Input Pin Of The Serial Port 1:  The serial data is sampled at the falling edge of the SCLK. The MSB is coming immediately after the falling of FR_SP1 signal. |

| 6,20,37<br>50,77,80,<br>89,107,<br>118,123 | 6,20,37<br>50,80,89<br>107,118,<br>123 | 6,20,37<br>50,77,80,<br>89,107,<br>118,123 | GND                                 | Р   | Ground                                                                                                                                                              |

| 22,<br>23,<br>24,<br>25                    |                                        |                                            | OUTP3,<br>OUTP2,<br>OUTP1,<br>OUTP0 | 0   | Modem Control Output  For external modem, these pins are bit7~4 of the modem control output. Memory address mapping of the controller is C800H.                     |

| 29,<br>30,<br>31,<br>32                    |                                        |                                            | INP3,<br>INP2,<br>INP1,<br>INP0     | I   | Modem Control Input:(External) These pins are bit3~0 of the modem control input. Memory address mapping of the controller is C800H.                                 |

| 33,45<br>67,94,<br>113,128                 | 33,45,<br>67,94,<br>113,128            | 33,45,<br>67,94,<br>113,128                | VDD                                 | Р   | +3.3V Power Supply                                                                                                                                                  |

| 13,74                                      | 13,74                                  | 13,74                                      | VCC                                 | Р   | +2.5V Power Supply                                                                                                                                                  |

| 34                                         | 34                                     | 34                                         | TEST2                               | I   | Test pin 2,normal ground                                                                                                                                            |

| 35                                         | 35                                     | 35                                         | TEST3                               | I   | Test pin 3,normal ground                                                                                                                                            |

| 36                                         |                                        |                                            | RESET                               | I   | Reset: An active high signal used to reset the DM6588.                                                                                                              |

| 42                                         | 42                                     | 42                                         | XTAL1                               |     | Crystal Oscillator Input                                                                                                                                            |

| 43     | 43     | 43     | XTAL2      | 0      | Crystal Oscillator Output                                             |  |  |  |

|--------|--------|--------|------------|--------|-----------------------------------------------------------------------|--|--|--|

| 46     | 46     | 46     | /PWR       | 0      | Controller Program Write Enable:                                      |  |  |  |

|        |        |        | ,          |        | This pin is used to enable FLASH ROM                                  |  |  |  |

|        |        |        |            |        | programming.                                                          |  |  |  |

| 48     | 48     | 48     | TD_SP1     | 0      | Data Output Pin Of Serial Port 1                                      |  |  |  |

|        |        |        |            |        | The serial data is clocked out through this pin                       |  |  |  |

|        |        |        |            |        | according to the rising edge of SCLK. The MSB is                      |  |  |  |

|        |        |        |            |        | sent immediately after the falling edge of the                        |  |  |  |

|        |        |        |            |        | FR_SP1 signal.                                                        |  |  |  |

| 49     | 49     | 49     | CA16       | 0      | Bank Switch Control:                                                  |  |  |  |

| 47     | 47     | 47     | CA17       |        | These signals are used to switch external program                     |  |  |  |

|        |        |        |            |        | memory between banks.                                                 |  |  |  |

|        |        |        |            |        | CA16 CA17                                                             |  |  |  |

|        |        |        |            |        | Bank 0 0 0                                                            |  |  |  |

|        |        |        |            |        | Bank 1 1 0                                                            |  |  |  |

|        |        |        |            |        | Bank 2 0 1                                                            |  |  |  |

|        |        |        |            |        | Bank 3 1 1                                                            |  |  |  |

| 51     |        |        | T0         |        | Controller Counter 0 Input                                            |  |  |  |

| 52     |        |        | T1         |        | Controller Counter 1 Input                                            |  |  |  |

| 57     | 76     | 76     | /RI        | l<br>· | Ring Signal Input                                                     |  |  |  |

| 76     | 57     | 57     | TxSCLK*2   | l      | TxDSP Interrupt 1 Input                                               |  |  |  |

| 58     | 58     | 58     | /DTR       | l      | DTR Input Pin (P1.1)                                                  |  |  |  |

| 59     | 59     | 59     | /OH        | 0      | Hook Relay Control (P1.2)                                             |  |  |  |

| 60     | 60     | 60     | /VOICE     | 0      | Voice Relay Control. Modem Control Output                             |  |  |  |

|        |        |        |            |        | (memory map is bit 3 of DAA at memory address                         |  |  |  |

|        |        |        |            |        | D000H)                                                                |  |  |  |

| 61-63  | 61-63  | 61-63  | EEPROM 1-3 | I/O    | EEPROM Control Pins (P1.4-P1.6)                                       |  |  |  |

| 66     |        |        | /LCS       | l      | Loop Current Detection. Modem Input Control:                          |  |  |  |

|        |        |        | 2011/      |        | This pin is mapped to bit0 of address D000H.                          |  |  |  |

| 79     | 66     | 66     | SCLK       | l      | Reference Clock For Serial Port 1 And Serial                          |  |  |  |

| 68     |        |        | RXD        | ı      | Port 2 Controller Serial Port Data Input                              |  |  |  |

| 69     |        |        | TXD        | 0      | Controller Serial Port Data Input  Controller Serial Port Data Output |  |  |  |

| 70     | 70     | 70     | RxSCLK     |        | Controller Serial Fort Data Output                                    |  |  |  |

|        |        |        |            | I      | Rx DSP Interrupt 3 Input                                              |  |  |  |

| 71     | 71     | 71     | /PSEN      | 0      | Controller Program Store Enable:                                      |  |  |  |

|        |        |        |            |        | This output goes low during a fetch from external                     |  |  |  |

|        |        |        |            |        | program memory.                                                       |  |  |  |

| 72     | 72     | 72     | /WR        | 0      | Controller External Data Memory Write Control                         |  |  |  |

| 73     | 73     | 73     | /RD        | 0      | Controller External Data Memory Read Control                          |  |  |  |

| 78     |        |        | DSPRxD     | 0      | Modem Received Data :(External)                                       |  |  |  |

|        |        |        |            |        | Shifted out to the EIA port through this pin                          |  |  |  |

|        |        |        |            |        | according to the rising edge of RXDCLK.                               |  |  |  |

| 117    | 117    | 117    | TEST1      |        | Test pin 1, normal ground                                             |  |  |  |

| 81,82, | 81,82, | 81,82, | CA15,CA14, | 0      | Controller Address Bus                                                |  |  |  |

| 83,84, | 83,84, | 83,84, | CA13,CA12, |        |                                                                       |  |  |  |

| 85,86, | 85,86, | 85,86, | CA11,CA10, |        |                                                                       |  |  |  |

| 87,88  | 87,88  | 87,88  | CA9,CA8    |        |                                                                       |  |  |  |

| 90,91, | 90,91, | 90,91, | CA7 - CA0  | 0      | Controller Address Bus                                                |  |  |  |

Final Version: DM562P-DS-F01

February 02, 2004

|           |          |            |             | 1   |                                                  |

|-----------|----------|------------|-------------|-----|--------------------------------------------------|

| 92,93,    | 92,93,   | 92,93,     |             |     |                                                  |

| 95,96,    | 95,96,   | 95,96,     |             |     |                                                  |

| 97,98     | 97,98    | 97,98      |             |     |                                                  |

| 99,100,   | 99,100,  | 99,100,    | D7,D6,      | I/O | Controller Data Bus                              |

| 101,102,  | 101,102, | 101,102,   | D5,D4,      |     |                                                  |

| 103,104,  | 103,104, | 103,104,   | D3,D2,      |     |                                                  |

| 105,106   | 105,106  | 105,106    | D1,D0       |     |                                                  |

| 108       | 108      | 108        | FR_SP2      | I/O | Frame Signal Of Serial Port 2                    |

| 109       | 109      | 109        | FR_SP1      | I/O | Frame Signal Of Serial Port 1                    |

| 110       | 110      | 110        | /POR        | 0   | DSP Reset Output                                 |

| 111       | 111      | 111        | VOICE Se1 1 | 0   | Modem Control Output                             |

| 112       | 112      | 112        | VOICE Se1 2 |     | Memory map is bit 1-2 of DAA at memory address   |

|           |          |            |             |     | D000H                                            |

| 114       | 114      | 114        | CODEC_CLK   | 0   | 20.16MHz Clock Output For DM6580 Chip            |

| 115       | 115      | 115        | OSCO        | 0   | Optional Codec X'tal clock output                |

| 116       | 116      | 116        | OSCI        | I   | Optional Codec X'tal clock input                 |

| 117       | 117      | 117        | TEST1       | ı   | Test pin 1,normal ground                         |

| 119       | 119      | 119        | TD_SP2      | 0   | Data Output Pin Of Serial Port 2                 |

| 110       | '''      | 110        | 10_01 2     |     | The serial data is clocked out through this pin  |

|           |          |            |             |     | according to the rising edge of SCLK. The MSB is |

|           |          |            |             |     | sent immediately after the falling edge of the   |

|           |          |            |             |     | FR_SP2 signal.                                   |

| 120       | 120      | 120        | PS1         | 0   | Modem Control Port Select Output:                |

|           |          |            |             |     | Memory address mapping of the controller is      |

|           |          |            |             |     | D800H.                                           |

| 122       | 122      | 122        | EXT/INTB    | I   | Select Pin: Used to select internal or external  |

|           |          |            |             |     | operation.                                       |

|           |          |            |             |     | 0: internal modem, PCI or ISA.                   |

|           |          |            |             |     | 1: external modem                                |

|           |          |            |             |     |                                                  |

| 7,14,15,  |          | 7,8,       | NC          | N   | NC                                               |

| 16,17,26, |          | 14,15,16,  | -           |     |                                                  |

| 27,38,39, |          | 17,21,25,  |             |     |                                                  |

| 40,41,44, |          | 26,27,28,  |             |     |                                                  |

| 53,54,55, |          | 32,38,39,  |             |     |                                                  |

| 56,64,65, |          | 40,41,44,  |             |     |                                                  |

| 75,121,   |          | 51,52,53,  |             |     |                                                  |

| 124,125,  |          | 554,55,56, |             |     |                                                  |

| 124,123,  |          | 64,65,75,  |             |     |                                                  |

| 120,121   |          | 79,121,    |             |     |                                                  |

|           |          | 124,125,   |             |     |                                                  |

|           |          |            |             |     |                                                  |

|           |          | 126,127    |             |     |                                                  |

10

DM6588 Pin Description-ISA Interface only

| Pin No. | Pin Name | I/O | Description                                                                         |

|---------|----------|-----|-------------------------------------------------------------------------------------|

| 2-5,    | UD0-UD3, | I/O | Data Bus Signal:                                                                    |

| 9-12    | UD4-UD7  |     | These signals are connected to the data bus of the PC (or Host) I/O.                |

|         |          |     | They are used to transfer data between the PC and the DM6588.                       |

| 22-24   | UA0-UA2  | ı   | System Address:                                                                     |

|         |          |     | These signals are connected to the bus of PC (or Host) I/O. They are used to        |

|         |          |     | select the DM6588 offset UART I/O address.                                          |

| 29      | /IOWB    | I   | I/O Write:                                                                          |

|         |          |     | An active low input signal used to write data to the DM6588.                        |

| 30      | /IORB    | I   | I/O Read:                                                                           |

|         |          |     | An active low input signal used to read data from the DM6588.                       |

| 31      | /CSN     | ı   | Address Enable:                                                                     |

|         |          |     | This is an active low signal to enable the system address for DM6588.               |

| 36      | /RST     | I   | Reset:                                                                              |

|         |          |     | An active low signal used to reset the DM6588.                                      |

| 78      | IRQ      | 0   | Interrupt Request:                                                                  |

|         |          |     | The active pin will go high when an interrupt request is generated from the DM6588. |

# DM6588 Pin Description-PCI Interface only

| Pin No.     | Pin Name | I/O | Description                                                                        |

|-------------|----------|-----|------------------------------------------------------------------------------------|

| 78          | POWEROFF | 0   | Power Off when high                                                                |

| 121         | INT#     | 0   | PCI Interrupt Request                                                              |

|             |          |     | This signal will be asserted low when an interrupt condition as defined in         |

|             |          |     | CR5 is set and the corresponding mask bit in CR7 is not set.                       |

| 79          | PCLK     | I   | PCI System Clock                                                                   |

|             |          |     | This signal is the PCI bus clock that provides timing for all bus phases.          |

|             |          |     | The frequency is 33MHz.                                                            |

| 75          | PME#     | 0   | Power Management Event                                                             |

|             |          |     | The signal indicates that a power management event.                                |

| 124-127,2-5 | AD31-AD0 | I/O | PCI Address & Data Bus                                                             |

| 9-12,14-17  |          |     | These are the multiplexed address and data signals.                                |

| 29-32,38-41 |          |     | DM6588 will decode each address on the bus and respond if it is the target         |

| 51-56,64,65 |          |     | being addressed.                                                                   |

| 7           | IDSEL    | ı   | Initialization Device Select                                                       |

|             |          |     | For the accesses to the configuration address space, the device select             |

|             |          |     | Decoding is done externally and is signaled via this pin. This signal is asserted  |

|             |          |     | high during configuration read and write access.                                   |

| 8           | C/BE3#   | ı   | PCI Bus Command/Byte Enable                                                        |

| 18          | C/BE2#   |     | During the address phase, these signals define the bus command or the type         |

| 28          | C/BE1#   |     | of the bus transaction that will take place.                                       |

| 44          | C/BE0#   |     | During the data phase, these pins indicate which byte lanes contain valid data.    |

|             |          |     | C/BE0# applies to bit7~0 and C/BE3# applies to bit 31~24.                          |

| 19          | FRAME#   | I   | PCI Cycle Frame                                                                    |

|             |          |     | This signal is driven low by the master to indicate the beginning and duration     |

|             |          |     | of a bus transaction. It is deasserted when the transaction is in its final phase. |

| 21          | IRDY#    | 1   | PCI Initiator Ready                                                                |

|             |          |     | This signal is driven low when the master is ready to complete the current data    |

|             |          |     | phase of the transaction. A data phase is completed on any clock both IRDY#        |

|             |          |     | and TRDY# are sampled asserted.                                                    |

| 22          | TRDY#    | I/O | PCI Target Ready                                                                   |

|             |          | _   | This signal is driven low when the target is ready to complete the current data    |

|             |          |     | phase of the transaction. During a read, it indicates that the valid data is       |

|             |          |     | asserted. During write, it indicates that the target prepares to accept data.      |

| 23          | DEVSEL#  | I/O | PCI Device Select                                                                  |

|             |          |     | DM6588 asserts the signal low when it recognizes its target address after          |

|             |          |     | FRAME# is asserted.                                                                |

| 24          | STOP#    | I/O | PCI Stop                                                                           |

|             |          |     | This signal is asserted low by the target device to request the master device to   |

|             |          |     | stop the current transaction.                                                      |

| 25          | PERR#    | I/O | PCI Parity Error                                                                   |

| -5          |          |     | DM6588 will assert this signal low to indicate a parity error on any incoming      |

|             |          |     | data.                                                                              |

| 26          | SERR#    | 0   | PCI System Error                                                                   |

|             | JEININI  |     | This signal is asserted low when an address parity is detected with PCICS bit31    |

|             |          |     | enabled. The system error asserts two clock cycles after the address if an         |

|             |          |     | address parity error is detected.                                                  |

|             |          |     | address parity offer is detected.                                                  |

12 Final Version: DM562P-DS-F0

| 27 | PAR     | I/O | PCI Parity                                                                       |

|----|---------|-----|----------------------------------------------------------------------------------|

|    |         |     | This signal indicates even parity across AD0~AD31 and C/BE0#~C/BE3#              |

|    |         |     | including the PAR pin. It is stable and valid one clock after the address phase. |

| 36 | RST#    | I   | Reset:                                                                           |

|    |         |     | An active low signal used to reset the DM6588.                                   |

| 76 | RIN     | I   | Ring Signal Input for Auxiliary Power                                            |

| 77 | GND_AUX | Р   | Auxiliary Ground                                                                 |

13

### **DM6588 Functional Description**

#### 1. Operating Mode Selection

The DM6588 can be used in internal or external modem applications. When operating as an internal modem, the EXT/INTB input (pin 122) must be attached to ground, and vice versa ( VDD ) when operating as an external modem.

External mode is operated with host by UART. Internal mode can support parallel (ISA) and PCI interface to host. The TEST4 input (pin 1) is for ISA or PCI selection.

#### 2. Micro-controller Program Memory

The DM6588 supports two bank switch control pins to switch external program memory among four banks. The DM6588 can access a total of 256K of external program memory.

Address mapping:

bank0: 00000H - 0FFFFH bank1: 10000H - 1FFFFH bank2: 20000H - 2FFFFH bank3: 30000H - 3FFFFH

For bank switching, three instructions must be included in software.

#### Switch to bank1:

CLR P1.3 SETB P1.7

JMP BANK 1 ADDRESS

#### Switch to bank2:

CLR P1.7 SETB P1.3

JMP BANK 2 ADDRESS

#### Switch to bank3:

CLR P1.7 CLR P1.3

JMP BANK 3 ADDRESS

#### Return to bank 0:

SETB P1.7 SETB P1.3

JMP BANK 0 ADDRESS

#### 3. Micro-controller Power Down Mode

An instruction that sets the register PD (PCON.1) will cause the 80C32 to enter power down mode. There are three ways to wake up the 80C32

- (1) Positive pulse signal occurring at the reset pin of the 80C32

- (2) Negative pulse occurring at /RI (P1.0) of the 80C32

- (3) Programming the PnP Wake Up Controller Register.

#### 4. Enhanced Internal Direct Memory

There are two 128 byte banks of internal direct memory in the 80C32. The system uses the lower 128 bytes under normal conditions. Switching to the upper bank is achieved by loading register 8FH.1 (SFR of the 80C32) with 1. Switching to the lower bank can be achieved by loading the same register with 0.

#### 5. Re-flash Program Memory

By setting 8FH.2 the system can switch program and data memory. If the system uses FLASH memory as program memory this function is used to re-flash program code by downloading the program to data memory then switching them.

#### Example:

SETB 8FH.2 LJMP 0000H

#### 6. Micro-controller I/O Description

**MODEM expansion port: Address C800H (external only)**

| Bit7 | Bit6 | bit5 | bit4 | bit3 | bit2 | bit1 | bit0 |

|------|------|------|------|------|------|------|------|

| OUT  | OUT  | OUT  | OUT  | INP3 | INP2 | INP1 | INP0 |

| P3   | P2   | P1   | P0   |      |      |      |      |

Bit0 to Bit3: read only Bit4 to Bit7: write only

### Modem Output Port 1 Register: Address D000H

#### Write only

| Bit7 | bit6 | bit5 | bit4 | Bit3   | bit2  | bit1  | bit0 |

|------|------|------|------|--------|-------|-------|------|

|      |      |      |      | /Voice | Voice | Voice | /POR |

|      |      |      |      |        | -sel2 | -Sel1 |      |

These 4 bits control the DM6588 output ports.

<sup>\*</sup> For detailed information about the micro-controller, refer to the *Programmer's Guide to 8032*.

Modem Output Port 2 Register: Address D800H

Write only

| bit7 | bit6 | bit5 | bit4 | bit3 | bit2 | bit1 | bit0 |

|------|------|------|------|------|------|------|------|

|      |      |      |      |      | /MUT | /PUL | /CID |

|      |      |      |      |      | E    | SE   |      |

These 3 bits control the DM6588 output ports.

**Memory Mapping of Micro-controller 80C32:**

| Address | Description                                  | External | Internal |

|---------|----------------------------------------------|----------|----------|

| C800H   | GPIO OUTP3-OUTP0(Bit7~4);INP3~INP0(Bit3~0)   | Y        | N        |

| D000H   | DAA Port                                     | Y        | Υ        |

| D400H   | UART Clock Register                          | N        | Υ        |

| D800H   | PS1 Port (Modem hybrid circuit control port) | Υ        | Υ        |

| DC0XH   | HDLC registers                               | Y        | Υ        |

| E000H   | Modem UART Status Register                   | N        | Υ        |

| E400H   | /RUCS Port(RX DSP Dual Port Registers)       | Υ        | Υ        |

| E800H   | Modem LED Output Port UD7~UD0                | Y        | N        |

| EC00H   | UART Baud Generator Divisor Latch Register   | N        | Υ        |

| F000H   | /TUCS Port (TX DSP Dual Port Register)       | Υ        | Υ        |

| F80XH   | PCI Vender & Device ID Port Register         | N        | Υ        |

Final 15

#### 7. HDLC Description

#### HDLC RxDataBits Register: Address DC00H

Write only

Once the RxDataBit set to 1, the data in the RxBuffer will be transferred to RxFIFO. The transfer bit number is the same as the programming value of RxDataBits Register.

#### HDLC RxBuffer: Address DC01H

Write only

Receive data will be written to the RxBuffer and will be input to the RxHDLC circuit. The RxBuffer is 16 bytes wide.

#### HDLC RxFiFo: Address DC01H

Read only

After the data has been passed from the RxBuffer to the RxHDLC circuit, the RxHDLC circuit will remove the 7eH patterns and transfer the results to the RxFIFO. There RxFIFO is 21 bytes wide.

#### HDLC TxDataBits Register: Address DC02H

Write only

Data written to TxDataBits will be presented to the TxFIFO. The data in TxFIFO will be transferred to TXHDLC circuit. The transfer bit number is the same as the value of TxDataBits register. If the TxFIFO is empty , a 7e pattern will be loaded to the TxFIFO. If TxFIFO is not empty and the data frame has the pattern of five consecutive "1", then the TXHDLC circuit will insert "0" automatically.

#### HDLC TxFiFo Register: Address DC03H

Write only

The original HDLC frame data will be loaded to the TxFIFO, presented to the input of the TxHDLC circuit. The TxFIFO is 21 bytes wide.

#### HDLC TxBuffer: Address DC03H

Read only

According to TxDataBits, the TxHDLC circuit will transfer the same number data bits to the TxBuffer. The TxBuffer is 16 bytes wide.

# HDLC CNTL/STATUS Register: Address DC04H

Bit0:TxReady0

16

0: indicates the data in the TxFIFO has deceased to zero and the HDLC circuit has transferred the 1st 7eH pattern.

1:indicates that the TxFIFO data is greater than or equal to the threshold value.

Bit1:Rxdata

0: all the data in the RxBuffer has been read.

1:Programed by software to indicate that all data in the RxDataBits register has been written to the RxBuffer.

Bit2:TxFIFO Threshold

0: TxFIFO threshold No. = 11 1: TxFIFO threshold No. =16

Bit3:TxFiFo Status

0:data No. in TxFIFO >= threshold 1:data No. in TxFIFO <= threshold

Bit4:Txdata

0:A write action to TxDataBites register will clear this bit.

1:Bit No. in TxBuffer = TxDataBits register.

Bit5: RxFIFO empty

0:data bytes No. in RxFIFO <>0 1:data bytes No. in RxFIFO = 0

Bit6: Reset

0:Normal state 1:reset HDLC circuit

# Zero Deletion In \_ buffer register: Address DC08H

write only

Controller write the original data to this temp buffer.

# Zero Deletion Out $\_$ buffer register: Address DC08H

read only

Controller read the result data from this buffer

# Zero Deletion Status/Rst register: Address DC09H

Bit0: data ready flag (read only)

1:data has been load to out \_ buffer. (clear automatically by a read from out buffer)

0: data has not been load to out \_ buffer.

Bit1: frame end flag (read only)

Final Version: DM562P-DS-F01

|       | 1:Indicate end of HDLC frame (clear by a rese | эt |

|-------|-----------------------------------------------|----|

| actio | n)                                            |    |

Bit2: fram ready flag (read only)

1:CRC check ok. 0:CRC check fail.

Bit3: In \_ buffer empty flag

1:In \_ buffer empty (clear automatically by a

write to In \_buffer)

0:In \_ buffer not empty

Bit7: reset bit (write only)

1:software reset

CRCL register: Address DC0AH (read only)

CRCH register: Address DC0BH (read only)

# 8. Micro-controller Control Register for Internal Mode

#### **UART Clock (internal mode only)**

The internal clock of the virtual UART logic is fixed at 1.8432MHz. The clock is derived from an external 30MHz crystal. The UART 1.8432MHz clock will be obtained by division. When the operating frequency of the DM6588 controller changes, the divider should be changed accordingly. This divider is specified by the Configuration Register which can be written by the DM6588 controller. The address mapping of the register is D400H: (DM6588 controller memory mapping)

Bit 0: Always 0.

Bit 6-1: define the clock divider range from 2 to 64 (even number).

Bit 7: Not used.

### **UART Clock Register: (internal mode only)**

Address D400H Reset State: 06H

Write Only

| bit7 | bit6 | bit5 | bit4 | bit3 | bit2 | bit1 | bit0 |

|------|------|------|------|------|------|------|------|

| Χ    | dat6 | dat5 | dat4 | dat3 | dat2 | dat1 | 0    |

# **UART Baud Generator Divisor Latch Register:** Address EC00H (internal mode only)

Read only

Final

| bit7 |      |      |      |      |      |      |      |

|------|------|------|------|------|------|------|------|

| dat7 | dat6 | dat5 | dat4 | dat3 | Dat2 | dat1 | dat0 |

By reading this register, the micro-controller can monitor the value of the low byte divisor latch of the virtual UART baud generator (see DLL in next section) and determine the baud rate clock itself.

# Modem Status Control Register (MSCR): Address E000H (internal mode only)

Write only

| bit7 | bit6 | bit5 | bit4 | bit3 | bit2 | bit1 | bit0 |

|------|------|------|------|------|------|------|------|

| 0    | 0    | 0    | 0    | /CTS | /DSR | /DCD | /RI  |

This register contains information about the line status of the modem. The available signals are Ring Detect (/RI), Carrier Detect (/DCD), Data Set Ready (/DSR) and Clear To Send (/CTS).

# 9. Host Control Register for Virtual 16550A UART (internal mode only)

Receiver Buffer (Read), Transmitter Holding Register (Write): Address: 0 (DLAB=0)

Reset State 00h

| bit7 | bit6 | bit5 | bit4 | bit3 | Bit2 | bit1 | Bit0 |

|------|------|------|------|------|------|------|------|

| dat7 | dat6 | dat5 | dat4 | dat3 | Dat2 | dat1 | Dat0 |

When this register address is read, it contains the parallel received data. Data to be transmitted is written to this register.

#### Interrupt Enable Register (IER): Address 1

Reset State 00h, Write Only

| bit7 | Bit<br>6 | bit<br>5 | bit4 | bit3                              | bit2                             | bit1                                        | bit0                         |

|------|----------|----------|------|-----------------------------------|----------------------------------|---------------------------------------------|------------------------------|

| 0    | 0        | 0        | 0    | Enable<br>Modem<br>Status<br>Intr | Enable<br>Line<br>Status<br>Intr | Enable<br>TX<br>Holding<br>Register<br>Intr | Enable<br>RX<br>Data<br>Intr |

This 8-bit register enables the four types of interrupts as described below. Each interrupt source can activate the INT output signal if enabled by this register. Resetting bits 0 through 3 will disable all UART interrupts.

Bit 0: This bit enables the Received Data Available

Version: DM562P-DS-F01

and timeout interrupts in the FIFO mode when set to logic 1.

Bit 1: This bit enables the Transmitter Holding Register Empty Interrupt when set to logic 1.

Bit 2: This bit enables the Receiver Line Status Interrupt when set to logic 1.

Bit 3: This bit enables the MODEM Status Interrupt when set to logic 1.

Bit 4-7: Not used

## Interrupt Identification Register (IIR): Address 2

Reset State 01h, Read only

| Bit7   | Bit6 | bit5 | bit4 | bit3  | bit2  | bit1  | bit0    |

|--------|------|------|------|-------|-------|-------|---------|

| FIFO   | 0    | 0    | 0    | D3:   | D2:   | D1:   | D0:     |

| Enable |      |      |      | INTD2 | INTD1 | INTD0 | int     |

|        |      |      |      |       |       |       | Pending |

In order to provide minimum software overhead during data transfers, the virtual UART prioritizes interrupts into four levels as follows: Receiver Line Status (priority 1), Receiver Data Available (priority 2), Character Timeout Indication (priority 2, FIFO mode only), Transmitter Holding Register Empty (priority 3), and Modem Status (priority 4).

The IIR register gives prioritized information regarding the status of interrupt conditions. When accessed, the IIR indicates the highest priority interrupt that is pending.

Bit 0: This bit can be used in either a prioritized interrupt or polled environment to indicate whether an interrupt is pending. When this bit is a logic 0, an interrupt is pending, and the IIR contents may be used as a pointer to the appropriate interrupt service routine. When bit 0 is a logic 1, no interrupt is pending, and polling (if used) continues.

Bit 1-2: These two bits of the IIR are used to identify the highest priority interrupt pending, as indicated in the table below.

Bit 3: In character mode, this bit is 0. In FIFO mode, this bit is set, along with bit 2, when a timeout interrupt is pending.

Bit 4-6: Not used

Bit 7: FIFO always enabled.

## Interrupt Identification Register (IIR): Address 2 (continued)

| D3 | D2 | D1 | D0 | <b>Priority Level</b> | Interrupt Type                                                           | Condition                                                                                                                  | Reset                                                                                                  |

|----|----|----|----|-----------------------|--------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|

| 0  | 0  | 0  | 1  | -                     | -                                                                        | -                                                                                                                          | -                                                                                                      |

| 0  | 1  | 1  | 0  | Highest               | Receiver Line<br>Status                                                  | Overrun Error, Parity Error,<br>Framing Error or Break<br>Interrupt                                                        | Reads the Line Status<br>Register                                                                      |

| 0  | 1  | 0  | 0  | Second                | Receiver Data Receiver Data Available of Available Trigger Level Reached |                                                                                                                            | Reads the Receiver Buffer<br>Register or the FIFO has<br>Dropped Below the<br>threshold value          |

| 1  | 1  | 0  | 0  | Second                | Character<br>Timeout Indication                                          | No characters have been read from or written to the Rx FIFO during programming time interval, and the Rx FIFO is not empty | Reads The Receiver Buffer<br>Register                                                                  |

| 0  | 0  | 1  | 0  | Third                 | Transmitter<br>Holding Register<br>Empty                                 | Ready to accept new data for transmission                                                                                  | Reads the IIR Register or<br>(if source of interrupt)<br>Writes To The Transmitter<br>Holding Register |

| 0  | 0  | 0  | 0  | Fourth                | Modem Status                                                             | Clear to Send, Data Set<br>Ready, Ring Indicator or<br>Data Carrier Detected                                               | Reads the Modem Status<br>Register                                                                     |

18 Final

#### FIFO Control Register (FCR): Address 2

Reset State 00h, write only

| bit7        | bit6  | bit5 | bit4 | bit3 | bit2   | bit1   | bit0   |

|-------------|-------|------|------|------|--------|--------|--------|

| <b>RCVR</b> | RCVR  | 0    | 0    | DMA  | TxFIFO | RxFIFO | FIFO   |

| Trig        | Trig  |      |      | Mode | Reset  | Reset  | Enable |

| (MSB)       | (LSB) |      |      |      |        |        |        |

This is a write only register at the same location as the IIR, which is a read only register. This register is used to enable the FIFOs, clear the FIFOs, set the RxFIFO trigger level, and select the type of DMA signal.

Bit 0: FIFO Enable, This bit is always high

Bit 1: Writing a 1 to FCR1 clears all bytes in the RxFIFO and resets the counter logic to 0.

Bit 2: Writing a 1 to FCR2 clears all bytes in the TxFIFO and resets the counter logic to 0.

Bit 3: Setting FCR3 to 1 will cause the RXRDY and TXRDY pins to change from mode 0 to mode 1 if FCR0 = 1.

Bit 4-5: Reserved

Bit 6-7: FCR6, FCR7 are used to set the trigger level for the RxFIFO interrupt.

| FCR7 | FCR6 | RxFIFO Trigger Level |  |  |

|------|------|----------------------|--|--|

| 0    | 0    | 01                   |  |  |

| 0    | 1    | 04                   |  |  |

| 1    | 0    | 08                   |  |  |

#### Line Control Register (LCR): Address 3

Reset State 00h, Write Only

| d |      | 10.10 | ,    |      | .,   |      |      |      |

|---|------|-------|------|------|------|------|------|------|

|   | bit7 | bit6  | bit5 | bit4 | bit3 | bit2 | bit1 | bit0 |

|   | DLAB | SBRK  | STP  | EPS  | PEN  | STB  | WLS1 | WLS0 |

This register is available to maintain compatibility with the standard 16550 register set, and provides information to the internal hardware that is used to determine the number of bits per character.

| WLS1 | WLS0 | Word Length |

|------|------|-------------|

| 0    | 0    | 5 bits      |

| 0    | 1    | 6 bits      |

| 1    | 0    | 7 bits      |

| 1    | 1    | 8 bits      |

Bit 0-1: WLS0-1 specifies the number of bits in each transmitted and received serial character.

Bit 2: STB specifies the number of stop bits in each transmitted character. If bit 2 is a logic 0, one stop bit is generated in the transmitted data. If bit 2 is a logic 1 when a 5-bit word length is selected via bits 0 and 1, one and a half stops are generated. If bit 2 is a logic 1 when either a 6-, 7- or 8-bit word length is selected, two stop bits are generated. The Receiver checks the first Stop-bit only, regardless of the number of Stop bits selected.

Bit 3: Logic 1 indicates that the PC has enabled parity generation and checking.

Bit 4: Logic 1 indicates that the PC is requesting an even number of logic 1s (even parity generation) to be transmitted or checked.

Logic 0 indicates that the PC is requesting odd parity generation and checking.

Bit 5: When bits 3, 4 and 5 are logic 1, the parity bit is transmitted and checked by the receiver as logic 0. If bits 3 and 5 are 1 and bit 4 is logic 0, then the parity is transmitted and checked as logic 1.

Bit 6: This is a Break Control bit. When it is set to logic 1, a break condition is indicated.

Bit 7: The Divisor Latch Access bit must be set to logic 1 to access the Divisor Latches of the baud generator during a read or write operation. It must be set to logic 0 to access the Receiver Buffer, the Transmitter Holding Register, or the Interrupt Enable Register.

Final 19

#### Modem Control Register (MCR): Address 4

Reset State 00h

| bit7 | bit6 | bit5 | bit4 | bit3 | bit2 | bit1 | bit0 |

|------|------|------|------|------|------|------|------|

| 0    | 0    | 0    | 0    | 0    | 0    | RTS  | DTR  |

Bit 0: This bit asserts a Data Terminal Ready condition that is readable via port P1.1 of the micro-controller 80C32. When bit 0 is set to logic 1, the P1.1 is forced to logic 0. When bit 0 is reset to logic 0, the P1.1 is forced to logic 1.

Bit 1: This bit asserts a Request To Send condition that is readable via port P3.4 of the micro-controller 80C32. When bit 1 is set to logic 1, the P3.4 is forced to logic 0. When bit 1 is reset to logic 0, the P3.4 is forced to logic 1.

#### Line Status Register (LSR): Address 5

Reset State 60h, Read only

| bit7 | bit6  | bit5 | bit4 | bit3 | bit2 | bit1 | bit0 |

|------|-------|------|------|------|------|------|------|

| RCV  | ETEMT | THRE | ВІ   | FE   | PE   | OE   | DR   |

This register provides status information to the host PC concerning character transfer. Bit 1-4 indicates error conditions that produce a Receiver Line Status interrupt whenever any of the corresponding conditions are detected. The Line Status Register is valid for read operations only.

Bit 0: Set to logic 1 when a received character is available in the RxFIFO. This bit is reset to logic 0 when the RxFIFO is empty.

Bit 1: An Overrun error will occur only after the RxFIFO is full and the next character has overwritten the unread FIFO data. This bit is reset upon reading the Line Status Register.

Bit 2: A logic 1 indicates that a received character does not have the correct even or odd parity as selected by the Parity Select bit. This error is set when the corresponding character is at the top of the RxFIFO. It will remain set until the CPU reads the LSR.

Bit 3: This bit is the Framing Error (FE) indicator. Bit 3 indicates that the received character did not have a valid stop bit. Bit 3 is set to a logic 1 whenever the stop bit following the last data bit or parity bit is detected as a zero bit (spacing level). The FE bit is reset whenever the CPU reads the contents of the Line Status Register. The FE error condition is associated with the particular character in the FIFO to which it applies. This error is revealed to the CPU when its associated character is at the top of the FIFO.

Bit 4: This bit is a Break Interrupt (BI) indicator. Bit 4 is set to logic 1 whenever the received data input is held in the Spacing (logic 0) state for longer than a full word transmission time (that is, the total time of Start bit + data bits + Parity + Stop bits). The BI indicator is reset whenever the CPU reads the contents of the Line Status Register. The BI error condition is associated with the particular character in the FIFO to which it applies. This error is revealed to the CPU when its associated character is at the top of the FIFO.

Bit 5: This bit is a Transmitter Holding Register Empty indicator. Bit 5 indicates that UART is ready to accept a new character for transmission. In addition, this bit causes the UART to issue an interrupt to the CPU when the Transmit Holding Register Empty Interrupt Enable is set high. The THRE bit is reset to logic 0 when the host CPU loads a character into the Transmit Holding register. In the FIFO mode, this bit is set when the TxFIFO is empty, and is cleared when at least 1 byte is written to the TxFIFO.

Bit 6: This bit is the Transmitter Empty indicator. Bit 6 is set to a logic 1 whenever the Transmitter Holding Register (THR) is empty, and is reset to a logic 0 whenever the THR contains a character. In FIFO mode, this bit is set to 1 whenever the transmit FIFO is empty.

Bit 7: In character mode, this bit is 0. In FIFO mode, this bit is set when there is at least one parity error, framing error, or break indication in the FIFO. If there are no subsequent errors in the FIFO, LSR7 is cleared when the CPU reads the LSR.

20 Final

### Modem Status Register (MSR): Address 6

Reset State bit 0-3: low, bit 4-7: Input Signal bit6 bit5 bit4 bit3 bit2 bit1 bit0 DSR CTS DDCD TERI DDSR DCTS DCD RI

This 8-bit register provides the current state of the control lines from the Modem to the CPU. In addition, four bits of the Modem Status Register provide change information. These bits are set to a logic 1 whenever a control input from the Modem changes state. They are reset to logic 0 whenever the CPU reads the Modem Status Register.

Bit 0: This bit is the Delta Clear to Send (DCTS) indicator. Bit 0 indicates that the CTS (MSR Bit 4) has changed state since the last time it was read by the CPU.

Bit 1: This bit is the Delta Data Set Ready (DDSR) indicator. Bit 1 indicates that the DSR (MSR Bit 5) has changed state since the last time it was read by the CPU.

Bit 2: This bit is the Trailing Edge of Ring indicator. Bit 2 indicates that the RI (MSR Bit 6) has changed from a low to a high state.

Bit 3: This bit is the Delta Data Carrier Detect (DDCD) indicator. Bit 3 indicates that the DCD (MSR Bti 7) has changed state.

Note: Whenever bit 0, 1, 2 or 3 is set to a logic 1, a Modem Status Interrupt is generated.

Bit 4: This bit reflects the value of MSR Bit 4 (CTS).

Bit 5: This bit reflects the value of MSR Bit 5 (DSR).

Bit 6: This bit reflects the value of MSR Bit 6 (RI).

Bit 7: This bit reflects the value of MSR Bit 7 (DCD).

#### Scratch Register (SCR): Address 7

Reset State 00h

This 8-bit Read/Write Register does not control the UART in any way. It is intended as a Scratch Pad Register to be used by the programmer to hold data temporarily.

#### Divisor Latch (DLL): Address 0 (DLAB = 1) Reset State 00h

| bit7 | bit6 | bit5 | bit4 | bit3 | bit2 | bit1 | bit0 |

|------|------|------|------|------|------|------|------|

| DAT7 | DAT6 | DAT5 | DAT4 | DAT3 | DAT2 | DAT1 | DAT0 |

This register contains baud rate information from the host PC. The PC sets the Divisor Latch Register

#### Divisor Latch (DLM): Address 1 (DLAB = 1) Reset State 00h

| Ì | bit7 | bit6 | bit5 | bit4 | bit3 | bit2 | bit1 | bit0 |

|---|------|------|------|------|------|------|------|------|

|   | DAT7 | DAT6 | DAT5 | DAT4 | DAT3 | DAT2 | DAT1 | DAT0 |

This register contains baud rate information from the host PC.

Note: Two 8-bit latches (DLL-DLM) store the divisor in 16-digit binary format. The desired baud rate can be obtained by dividing the 115200Hz clock by the divisor.

| Desired<br>Baud<br>Rate | Divisor<br>Value |

|-------------------------|------------------|

| 50                      | 2304             |

| 75                      | 1536             |

| 110                     | 1047             |

| 150                     | 768              |

| 300                     | 384              |

| 600                     | 192              |

| 1200                    | 96               |

| 2400                    | 48               |

| 4800                    | 24               |

| 9600                    | 12               |

| 19200                   | 6                |

| 38400                   | 3                |

| 57600                   | 2                |

| 115200                  | 1                |

Final Version: DM562P-DS-F01

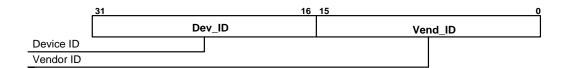

# 10. Micro-controller Control Register for PCI interface

# PCI Vender ID Low Byte Data Port: Address F800H (pci only)

Write only

This port configures PCI Vender ID low byte. (Offset 00 of PCI configuration register space)

# PCI Vender ID High Byte Data Port: Address F801H (pci only)

Write only

This port configures PCI Vender ID high byte. (Offset 01 of PCI configuration register space)

#### PCI Device ID Low Byte Data Port: Address F802H

Write only

This port configures PCI Device ID low byte. (Offset 02 of PCI configuration register space)

# PCI Device ID High Byte Data Port: Address F803H

Write only

This port configures PCI Device ID low byte. (Offset 00 of PCI configuration register space)

# PCI Subsystem Vender ID Low Byte Data Port: Address F804H (pci only)

Write only

This port configures PCI Subsystem Vender ID low byte. (Offset 2C of PCI configuration register space)

# PCI Subsystem Vender ID High Byte Data Port: Address F805H (pci only)

Write only

This port configures PCI Subsystem Vender ID high byte. (Offset 2D of PCI configuration register space)

# PCI Subsystem Device ID Low Byte Data Port: Address F806H

Write only

This port configures PCI Subsystem Device ID low

byte. (Offset 2E of PCI configuration register space)

# PCI Subsystem Device ID High Byte Data Port: Address F807H

Write only

This port configures PCI Subsystem Device ID low

# byte. (Offset 2F of PCI configuration register space) PCI Power Management New Capability: Address F808H, Bit 4 (pci only)

Write only

This bit configures if support PCI Power Management. (Offset 06 bit 4 of PCI configuration register space)

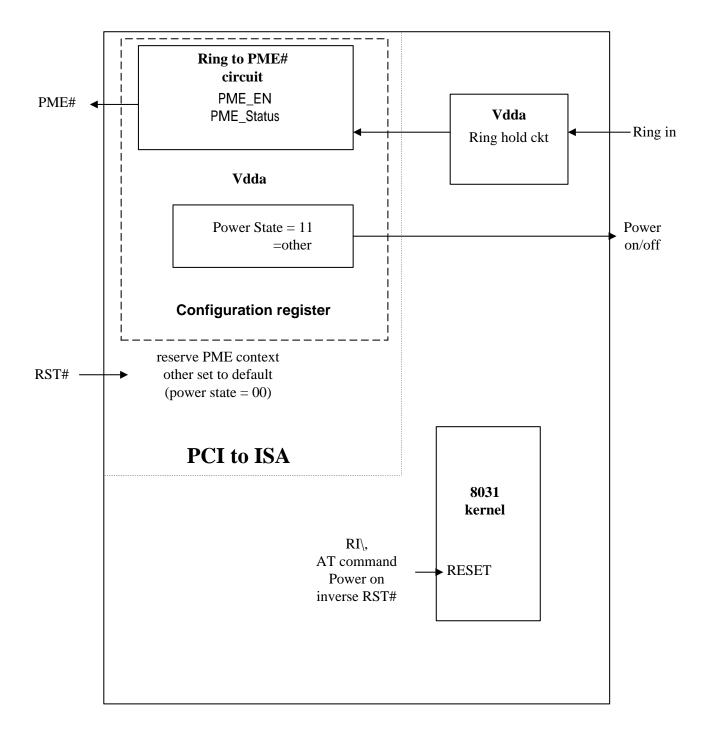

# PCI Power Management Power State: Address F809H, Bit[1..0] (pci only)

Write / Read

These bits configures PCI Power management Power State. (Offset 54 bit [1..0] of PCI configuration register space)

# PCI Power Management PME\_STATUS: Address F80AH, Bit 1

Write only

This bit configures PCI Power status. (Offset 55 bit 7 of PCI configuration register space)

# PCI Power Management PME\_EN: Address F80AH, Bit 0

Write only

This bit configures PCI if enable PME wake up (Offset 55 bit 0 of PCI configuration register space)

# PCI PME\_D3\_Support: Address F80BH, Bit 0

Write only

This port configures PCI if support PME wake up at D3 state. (Offset 53 bit [8..7] of PCI configuration register space)

22 Final

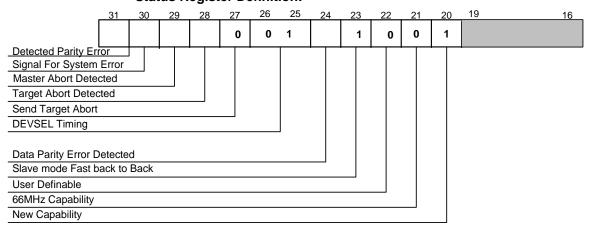

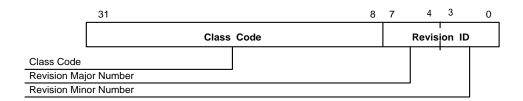

### 11. PCI Configuration Register Definition

The definitions of PCI Configuration Registers are based on the PCI specification revision 2.1 and provides the initialization and configuration information to operate the PCI interface in the DM6588. All registers can be accessed with byte,

word, or double word mode. As defined in PCI specification 2.1, read accesses to reserve or unimplemented registers will return a value of "0." These registers are to be described in the following sections.

**PCI Configuration Registers Mapping:**

| Description                | Identifier | Address   | Value of Reset |

|----------------------------|------------|-----------|----------------|

| P                          |            | Offset    |                |

| Identification             | PCIID      | 00H       | 6588A1282H     |

| Command & Status           | PCICS      | 04H       | 04100001H      |

| Revision                   | PCIRV      | 08H       | 07000210H      |

| Miscellaneous              | PCILT      | 0CH       | 00000000H      |

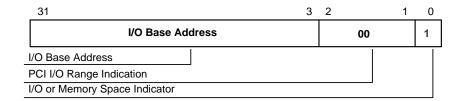

| I/O Base Address           | PCIIO      | 10H       | XXXXXXXx001    |

| Reserved                   |            | 14H - 28H |                |

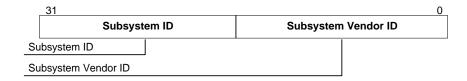

| Subsystem Identification   | PCISID     | 2CH       | undefined      |

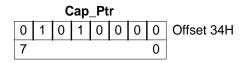

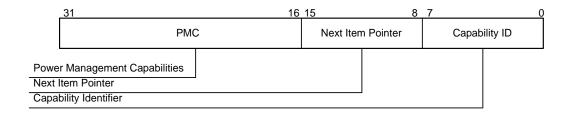

| Capability Pointer         | CAP_PTR    | 34H       | 00000050H      |

| Reserved                   |            | 38H       |                |

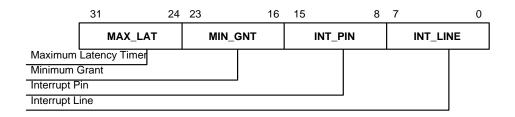

| Interrupt & Latency        | PCIINT     | 3CH       | 281401XXH      |

| Power Management Register  | PMR        | 50H       | 00110001H      |

| Power Management Control & | PMCSR      | 54H       | 00000000H      |

| Status                     |            |           |                |

Final 23

**Configuration Register Structure**

|              | Comigaration in   | egister otraotare |                    |     |  |  |  |

|--------------|-------------------|-------------------|--------------------|-----|--|--|--|

| Dev          | vice ID           | Vendo             | r ID               | 00H |  |  |  |

| Status (with | bit 4 set to 1)   | Comma             | and <u> </u>       | 04H |  |  |  |

| CI           | ass Code = 070002 |                   | Revisio            | 08H |  |  |  |

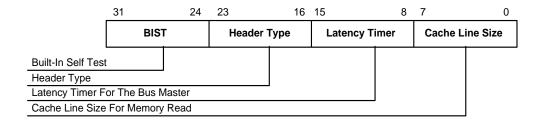

| BIST         | Header Type       | Latency Timer     | Cach Line Size     | 0CH |  |  |  |

|              | Bass Address      | Register CBIO     |                    | 10H |  |  |  |

|              | Rese              | erved             |                    | 14H |  |  |  |

|              |                   |                   |                    | 18H |  |  |  |

|              | Reser             | rved              |                    | 1CH |  |  |  |

|              |                   |                   |                    | 20H |  |  |  |

|              |                   |                   |                    | 24H |  |  |  |

|              |                   |                   |                    | 28H |  |  |  |

| Subsyste     | em ID             | Subsystem '       | 2CH                |     |  |  |  |

|              | Rese              |                   |                    | 30H |  |  |  |

|              | Reserved          |                   | Cap_Ptr            | 34H |  |  |  |

|              | Res               | erved             |                    | 38H |  |  |  |

| Max_Lat      | Min_Gnt           | Interrupt Pin = 1 | Interrupt Line     | зсн |  |  |  |

|              | R                 | eserved           |                    | 40H |  |  |  |

|              |                   |                   |                    |     |  |  |  |

| Reserved     |                   |                   |                    |     |  |  |  |

|              |                   |                   |                    |     |  |  |  |

| Power Manage | ment Capability   | Next Item Pointer | Capability ID      | 50H |  |  |  |

| Rese         | erved             | Power Management  | Control and Status | 54H |  |  |  |

|              |                   |                   |                    |     |  |  |  |

### **Key to Default**

In the register description that follows, the default column takes the form <Reset Value> Where:

<Reset Value>:

Bit set to logic oneBit set to logic zero

X No default value

<Access Type>:

RO = Read only

RW = Read/Write

R/C: means Read / Write & Write "1" for Clear.

\_WR = Controller Write \_RD = Controller Read

24 Final

### Identification ID (xxxxxx00 - PCIID)

| Bit   | Default | Туре | Description                                                                 |

|-------|---------|------|-----------------------------------------------------------------------------|

| 31:16 | 6588Ah  | RO   | The field identifies the particular device. Unique and fixed number for the |

|       |         | _WR  | DM6588 is 6588Ah. It is the product number assigned by DAVICOM.             |

| 15:0  | 1282h   | RO   | This field identifies the manufacturer of the device. Unique and fixed      |

|       |         | _WR  | number for Davicom is 1282h. It is a registered number from SIG.            |

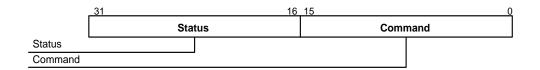

### Command & Status (xxxxxx04 - PCICS)

### **Status Register Definition:**

Final 25

| Bit   | Default | Туре      | Description                                                                                                                                                                                                                                                                 |

|-------|---------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31    | 0       | R/C       | Detected Parity Error The DM6588 samples the AD[0:31], C/BE[0:3]#, and the PAR signal to check parity and to set parity errors.                                                                                                                                             |

| 30    | 0       | R/C       | Signaled System Error This bit is set when the SERR# signal is driven by the DM6588. This system error occurs when an address parity is detected under the condition that bit 8 and bit 6 in command register below are set.                                                |

| 29    | 0       | R/C       | Master Abort Detected The DM6588 will never support the function                                                                                                                                                                                                            |

| 28    | 0       | R/C       | Target Abort Detected The DM6588 will never support the function                                                                                                                                                                                                            |

| 27    | 0       | RO        | Send Target Abort (0 For No Implementation) The DM6588 will never support the function.                                                                                                                                                                                     |

| 26:25 | 10      | RO        | DEVSEL Timing (10 Select Slow Timing) Slow timing of DEVSEL# means the DM6588 will assert DEVSEL# signal two clocks after FRAME# is sample "asserted."                                                                                                                      |

| 24    | 0       | R/C       | Data Parity Error Detected The DM6588 will never support the function                                                                                                                                                                                                       |

| 23    | 0       | RO        | Slave mode Fast Back-To-Back Capable (1 For Good Capability) The DM6588 will never support the function                                                                                                                                                                     |

| 22    | 0       | RO        | User-Definable-Feature Supported (0 For No Support)                                                                                                                                                                                                                         |

| 21    | 0       | RO        | 66 MHz Capable (0 For No Capability)                                                                                                                                                                                                                                        |

| 20    | 1       | RO<br>_WR | New Capabilities This bit indicates whether this function implements a list of extended capabilities such as PCI power management. When set this bit indicates the presence of New Capabilities. A value of 0 means that this function does not implement New Capabilities. |

| 19:16 | 0000    | RO        | Reserved                                                                                                                                                                                                                                                                    |

26 Final

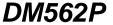

### **Command Register Definition:**

| Bit   | Default | Туре | Description                                                                                                                                                                                           |

|-------|---------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|